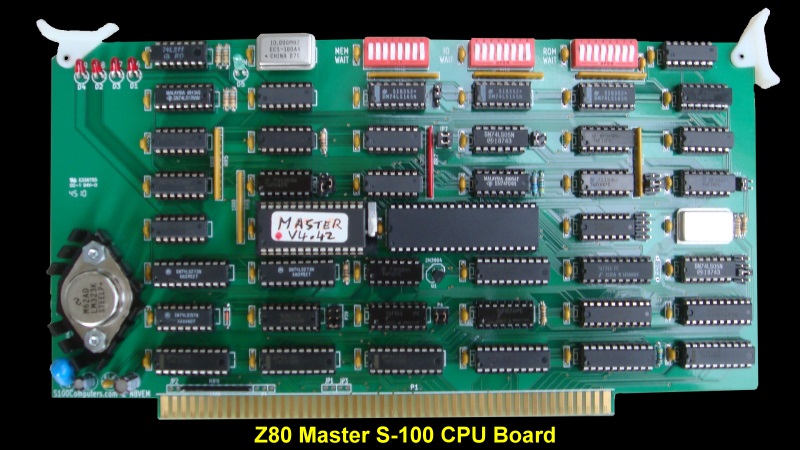

Final 10MHz Master Z80 CPU Board.

The final (V3) of this board is now completed and people have received boards.

Some minor tweaks of the above V2 prototype board were made. In particular we

removed the IMSAI front panel connector (top right hand corner). This allowed

considerable trace optimization. The IMSAI front panel would probably not work

with this board at these speeds anyway, besides the

SMB fulfills many of

these functions.

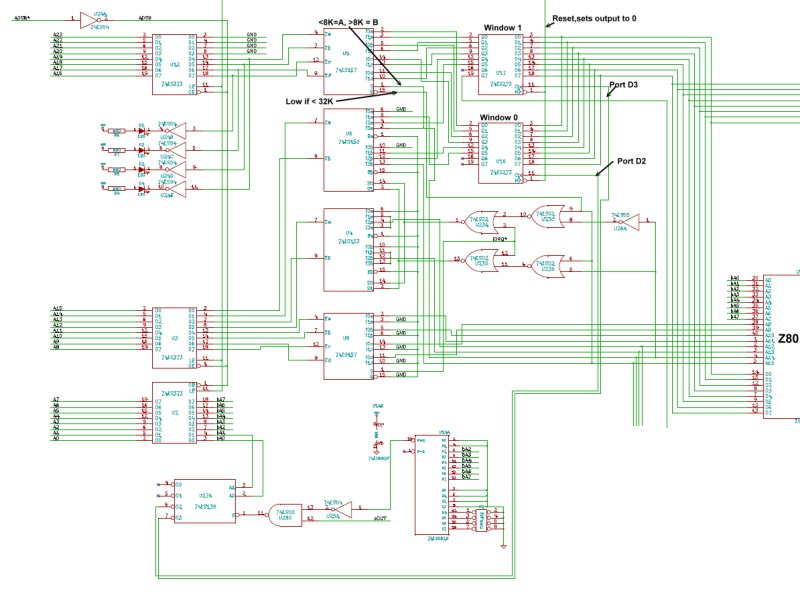

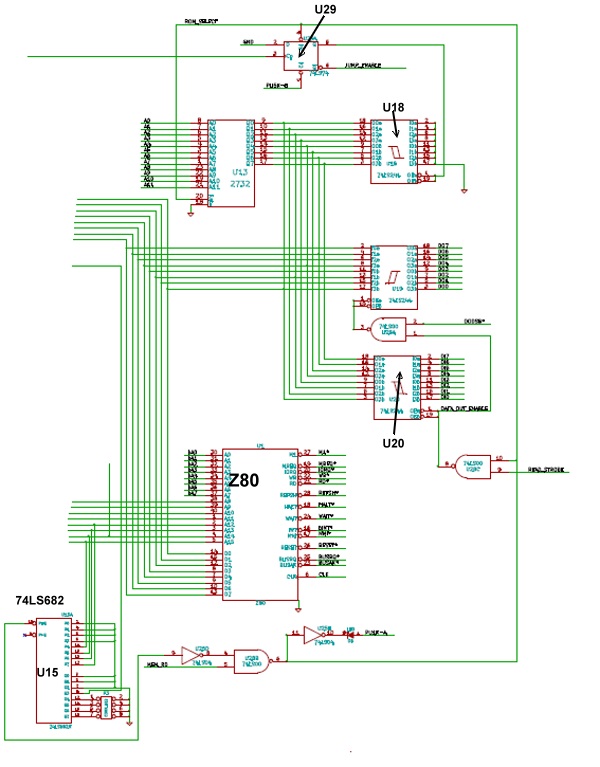

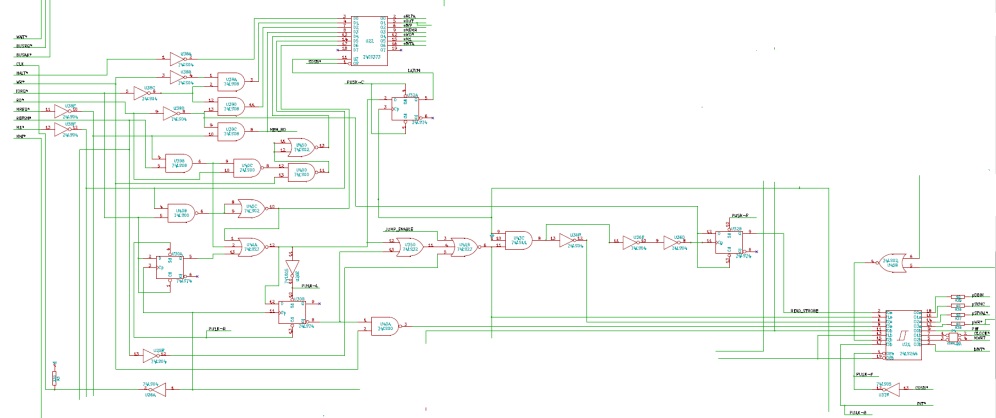

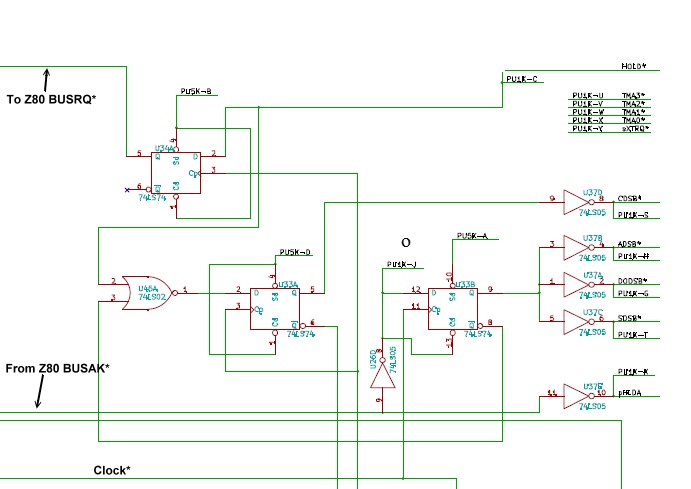

Here is a schematic of the

third Z80 Prototype board. The board layout

can be seen

here.

The board in my bus actually "works most of the time" at 11

MHz

However it's not completely reliable at these speeds. Some day I may try

tweaking the above chips some more. At 10MHz it's completely reliable. It

works fine too handing control over to an 8086 as a master/slave switch. It also

appears to work fine with the interrupts from the PIC/RTC board.

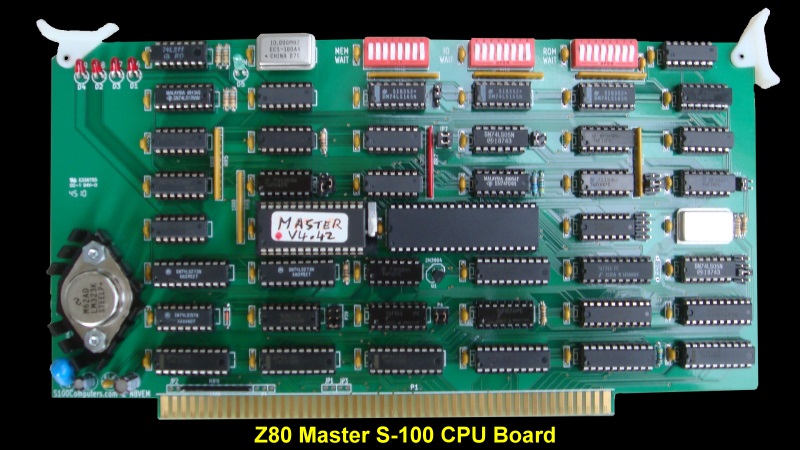

Here is a picture of the Final Z80 Master CPU Board.

Two very small errors exist on the board - resistor R41 is a

carry over from a previous version. It is connected to nothing. Ignore it. Also

C1 should be something like a 47uF Tantalum cap (25V) rather than a 0.33uF as

shown on the board silkscreen. Also note the large 3A voltage regulator is

close to the right hand side of the board. I found it neceassary to clip off two

of the "fins" so the card would easily slide into my card cage. I think

the square type heat sinks would be OK.

Unlike many of the other boards on this site you cannot build and check out the

board in stages. To start with however use a 2 or 4 MHz clock oscillator.

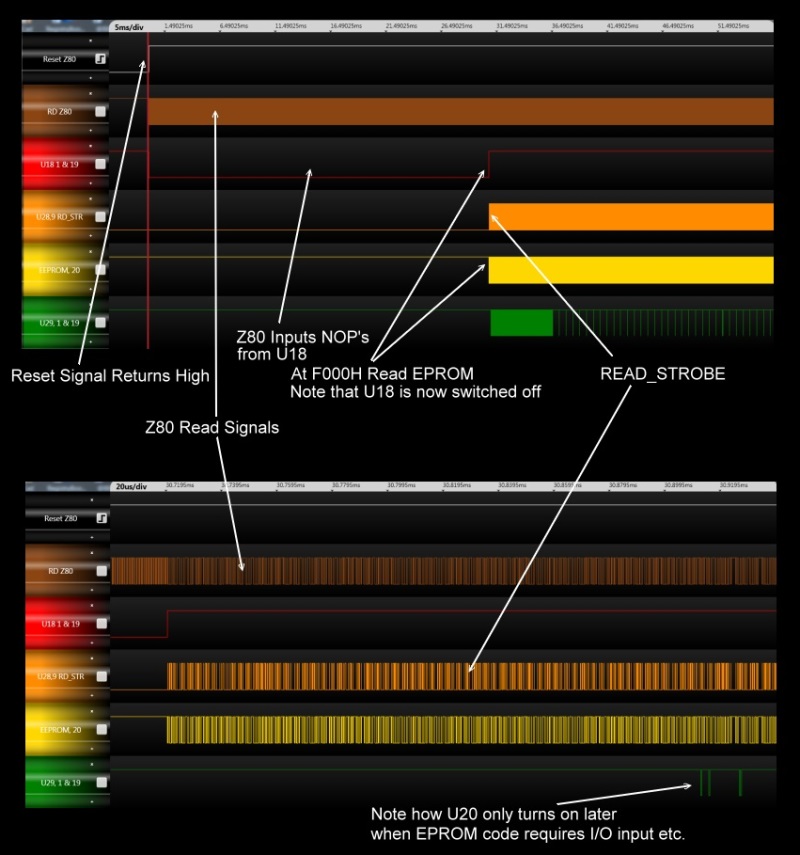

If your board does not come up at these speeds, change your Monitor code in

EPROM to one with an EPROM with just 76H's (HALT) and see if you can get the Z80

to always halt after a reset. If it does not, check the POC circuitry and see

above how the board steps through memory addresses to arrive at the boot EPROM

address. If you are using our

SMB none of the

jumpers JP4-7 need be used. Of course you can disable them on the SMB and

use them here if you like. Lastly don't expect this board to run at

10MHz

speeds in a non-terminated S-100 bus or with old/slow S-100 memory boards.

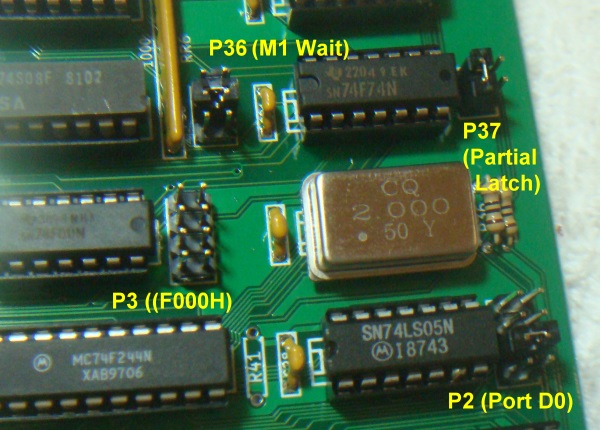

Note if you decide to use a EEPROM such as a Samsung MK28C64A 8KX8, you have to

place it at an 8 K boundary. So in high RAM this would be at E000H. If you want to use

E000H-FFFFH for your monitor then that's fine. More typically however you will

need only 4K for a monitor starting at say F000H to FFFFH. In this

situation you can either program the second 4K of the EEPROM's 8K space and

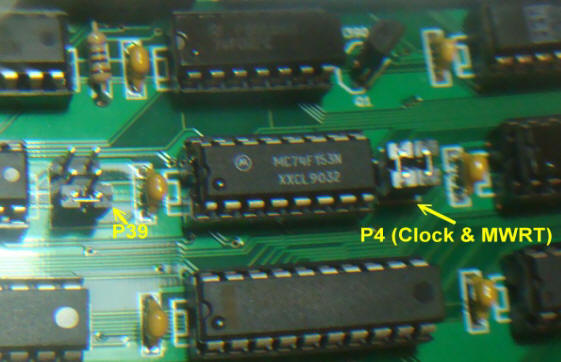

jumper JP8 1-2 and P39 5-6 (i.e. utilize A1 and A12) and set the POJ

jumper P3, to F000H,

or alternatively just program the lower 4K of the EEPROM's 8K space and force

the EEPROMS A12 line to low, so jumper JP8 10-2 as before, but jumper P39 3-4. BTW, you

can have a second completely different second monitor in the EEPROM switchable

to the upper or lower half of the EEPROM with jumpers P39 3-4 or 1-2.

You must also be sure to "burn" your monitor into the upper or lower half of the

EEPROM. (For the upper half, using a

Wellon VP-280

Programmer, the "Load Buffer Address" would be 1000H, the "File Address" is

F000H).

Hopefully this is not too confusing. If so, start with an old 2732 EPROM

and burn your initial monitor in that chip.

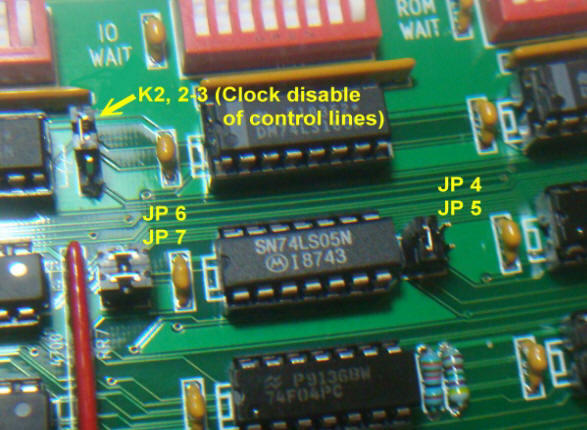

For a 10 MHz system with the 74Fxx or 74Sxx chips I mentioned above, here

are pictures of the jumpers to get you going.

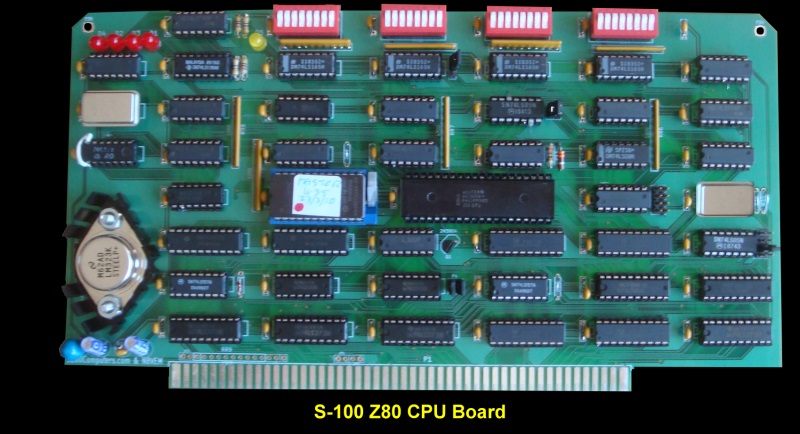

A Production S-100 Board.

Realizing that a number of people might want to utilize a board like this

together

with Andrew Lynch at N8VEM (see

here) we have

completed a run of these boards. We will collect names for a second

batch if needed. If

you have an interest in such a bare board, let Andrew know via e-mail at:-

lynchaj@yahoo.com

Please note all the above

clearly applies only to people who know what they are doing and can do

a little soldering and board assembly. There will be little hand holding

at this stage.

The links below will contain the most recent schematic of this board.

Note, it may change over time and some IC part or pin numbers may not correlate

exactly with the text in the article above.

MOST

CURRENT Z80 CPU BOARD SCHEMATIC

(V2, FINAL, 02/28/2010)

MOST

CURRENT Z80 CPU BOARD LAYOUT (V2, FINAL,

02/28/2010)

Other pages describing my S-100

hardware and software.

Please click

here

to continue...

This page was last modified

on 09/16/2011

.jpg)